# Energy-aware Scheduling and Fault Tolerance Techniques for the Exascale Era

**IV Congreso REDU**

**December 1**st, 2016

Laércio Lima Pilla

laercio.pilla@ufsc.br

Federal University of Santa Catarina, Brazil

#### Agenda

### **EnergySFE Project**

## Global Scheduling

problems + research + interests

#### **Fault Tolerance**

problems + research + interests

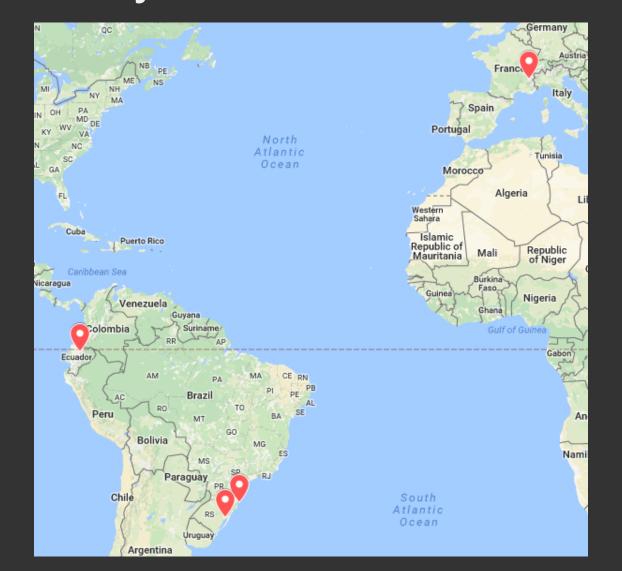

#### STIC-AmSud Project Grant 99999.007556/2015-02

#### Members

**Enrique Vinicio Carrera - EC**

François Broquedis - FR

Frédéric Desprez - FR

Jean-François Méhaut - FR

Laércio Lima Pilla - BR

Lucas Mello Schnorr - BR

Márcio Bastos Castro - BR

**Mario Antônio Dantas - BR**

Pablo Francisco Ramos - EC

Paolo Rech - BR

Philippe O. A. Navaux - BR

Vanessa C. Vargas - EC

# Energy-aware Scheduling and Fault Tolerance Techniques for the Exascale Era

Increasing performance with limited energy

#### **Research Questions**

1. How to schedule tasks and threads that compete for resources with different constraints while considering the complex hierarchical organization of future Exascale supercomputers?

#### **Research Questions**

2. How to tolerate faults without incurring in too much overhead in future Exascale supercomputers?

#### Research Questions

3. How scheduling and fault tolerance approaches can be adapted to be energy-aware?

## Global Scheduling

problems + research + interests

## objectives

shortest execution time

highest throughput

highest utilization rate

fairness

•••

#### load imbalance

poor initial mapping

load dynamicity

platform sharing

heterogeneous platforms

DVFS changes

...

#### communication slowdown

poor initial mapping

complex communication patterns

hierarchical machine topologies

platform sharing

heterogeneous platforms

## energy wastage

long computing times

low resource usage

excessive data movement

slow scheduling algorithms

What we want with scheduling balanced loads optimized communications fast scheduling algorithms least migrations possible

# Periodic load balancing principle of persistence

topology-aware load balancing energy-aware load balancing

topology-aware load balancing

**NucolB**

greedy algorithm + NUMA node latency

**HwTopoLB**

refinement algorithm + latency & bw + convergence

#### HierarchicalLB

LB at node level and at whole machine level

**Application: Ondes3D**

irregular loads

dynamic loads

**Application: Ondes3D**

irregular loads

dynamic loads

#### **Application: Ondes3D**

OD = overdecomposition (16 tasks / core)

#### **Application: Ondes3D**

**OD** = overdecomposition (16 tasks / core)

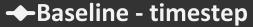

◆Baseline - timestep ◆OD - average PU load ◆HwTopoLB - timestep ◆NucoLB - timestep

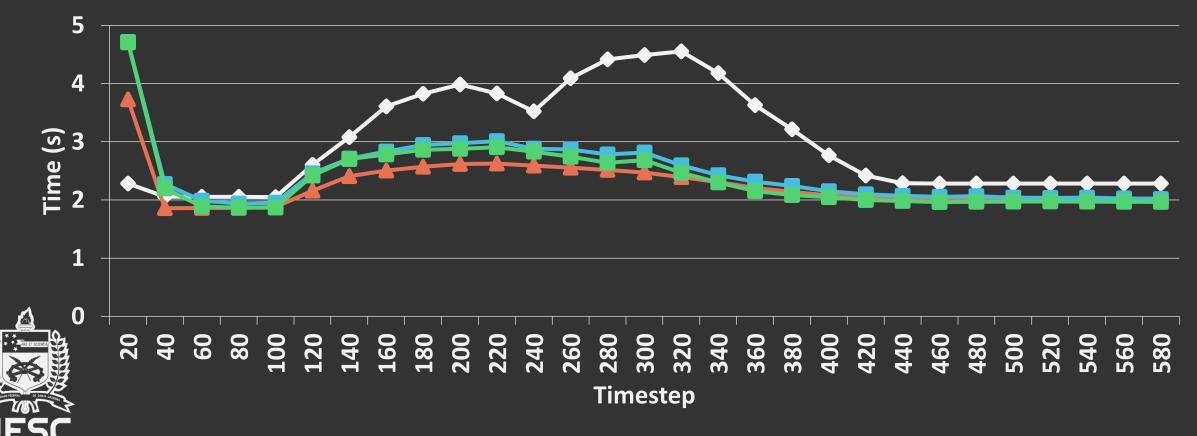

**Application: LeanMD**

Weak scalability: Total execution time

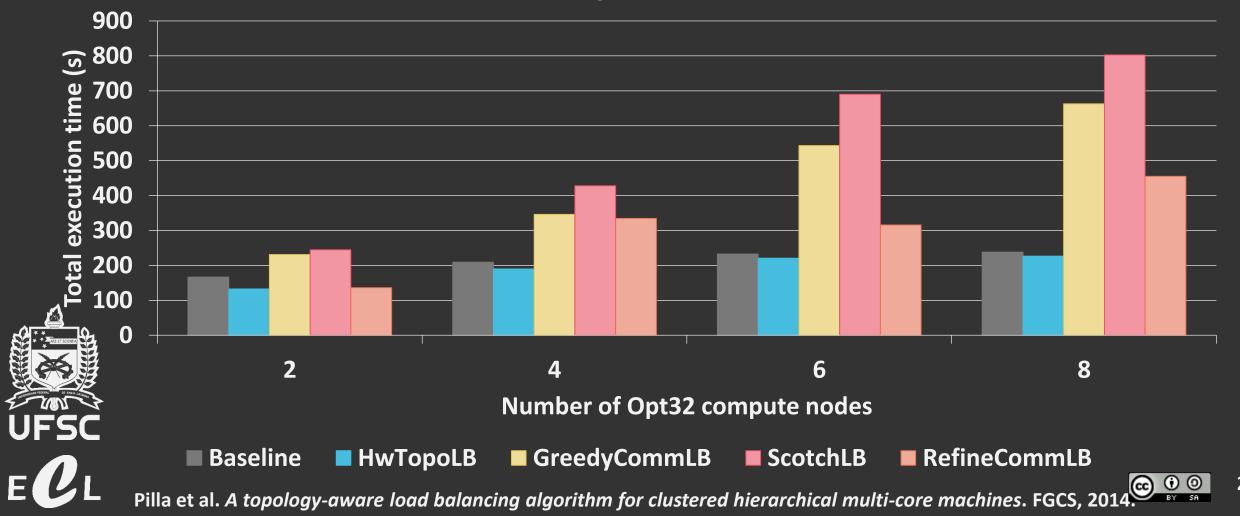

Strong scalability: LeanMD

Speedup over the baseline on 2 CNs

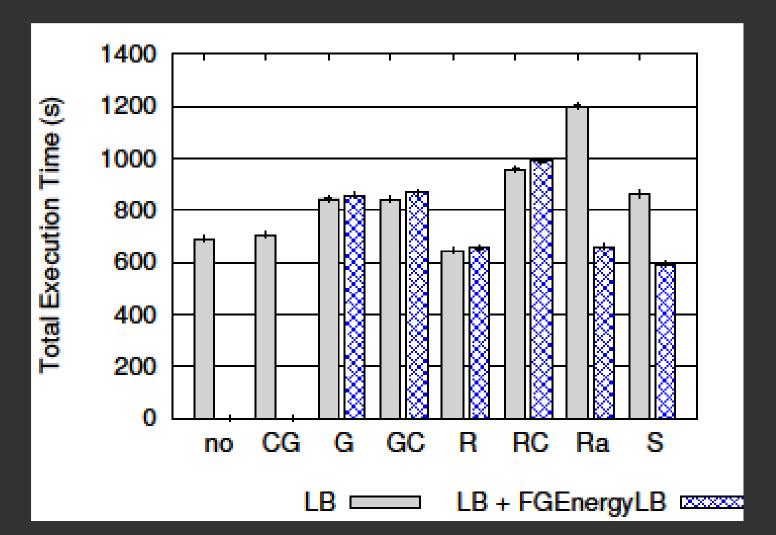

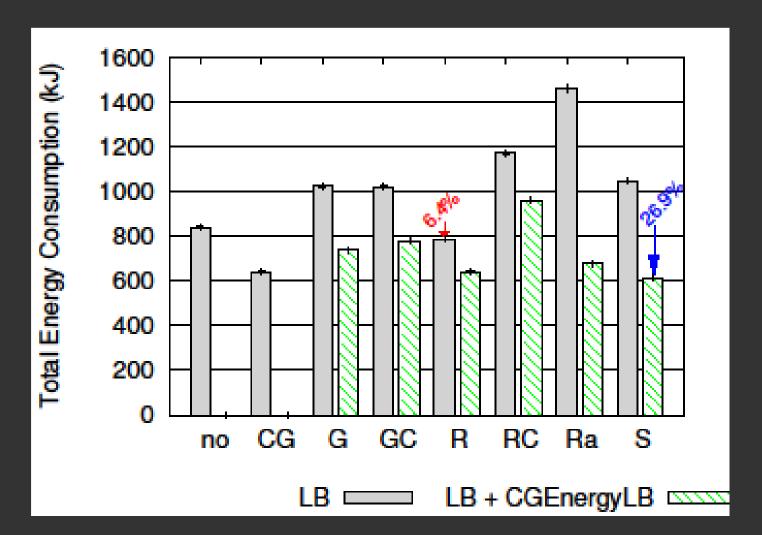

energy-aware load balancing

LB + DVFS on underloaded resources

#### Fine-Grained EnergyLB

per core

#### Coarse-Grained EnergyLB

per socket + hierarchical algorithm

Example: Lulesh + FG EnergyLB

**Example: Lulesh + FG EnergyLB**

#### Global Scheduling Interests

- + hierarchical algorithms [+ energy]

- + distributed algorithms [+ energy]

- + platforms for experiments [+ energy]

- + applications

## Fault Tolerance

problems + research + interests

failure: systems stops working as expected fault → error → failure

#### **Fault Tolerance**

use redundancy to stop failures from occurring

usual fault tolerance schemes

checkpoint & restart

cannot notice corrupted data

#### duplication with comparison

expensive in resource (time & energy)

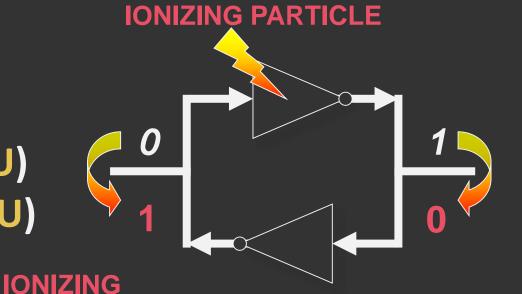

**Soft Errors:** the device is not permanently damaged, but a particle may generate:

**PARTICLE**

Logic

One or more bit-flips

Single Event Upset (SEU)

Multiple Bit Upset (MBU)

Transient voltage pulse Single Event Transient (SET)

FF

#### **Silent Data Corruption**

data caches

register files

**ALU**

scheduler

#### Crash

instruction cache scheduler

PCIe bus

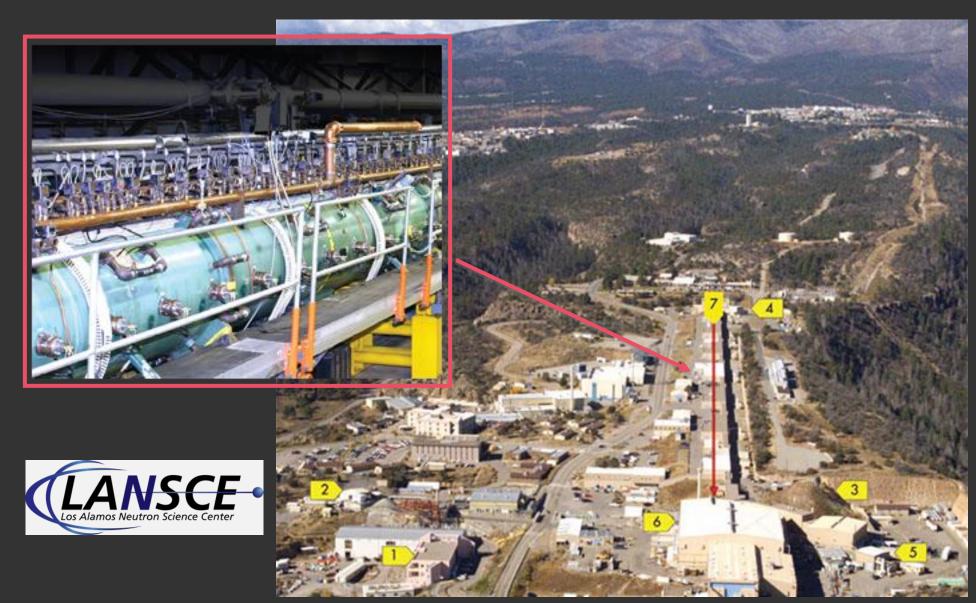

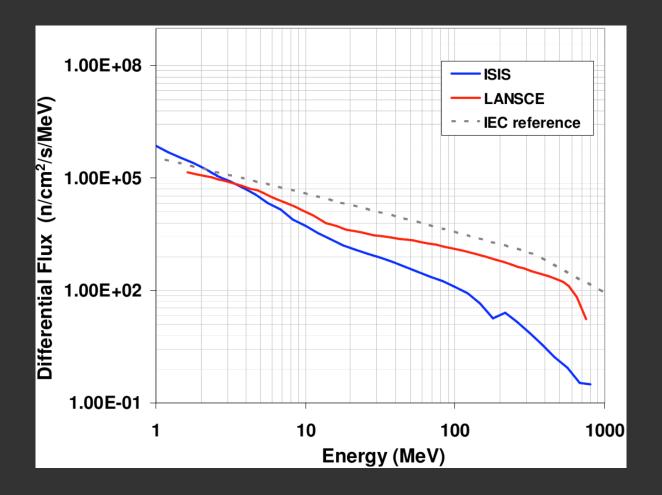

## @LANSCE 1.8x10<sup>6</sup> n/(cm<sup>2</sup> h) @NYC 13 n/(cm<sup>2</sup> h)

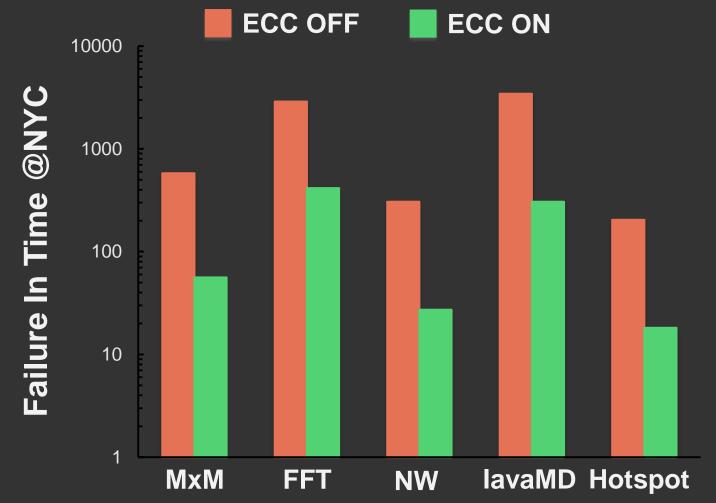

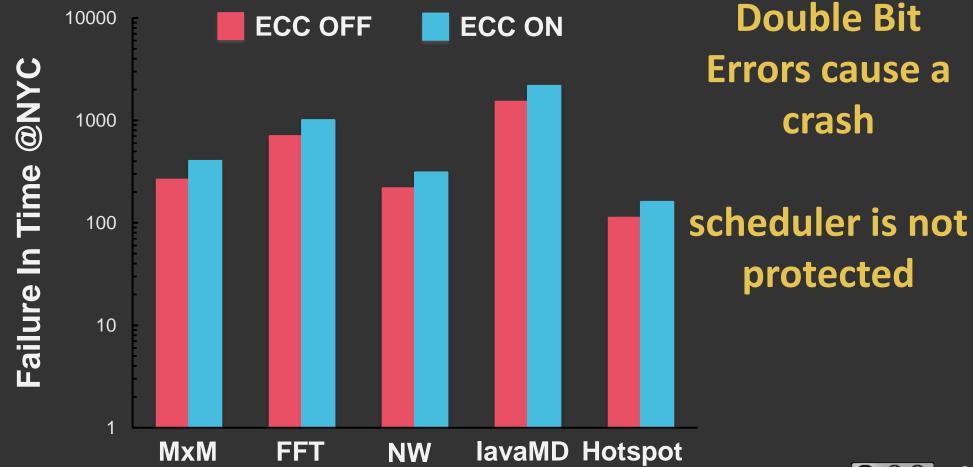

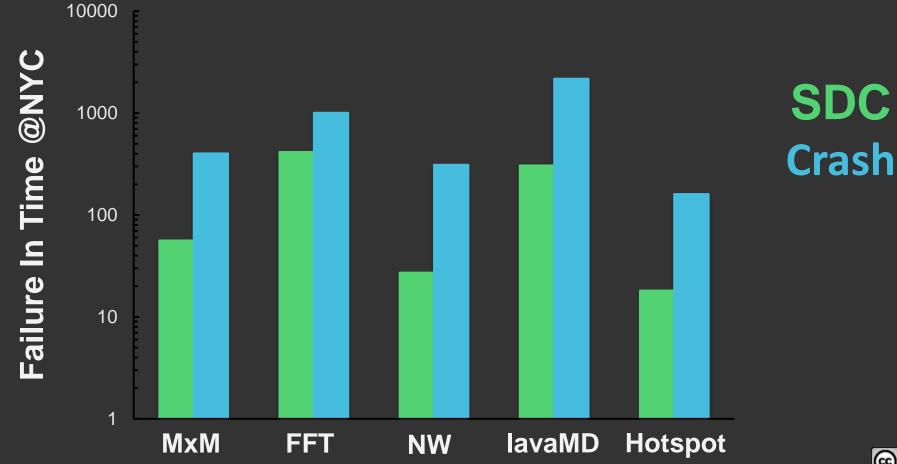

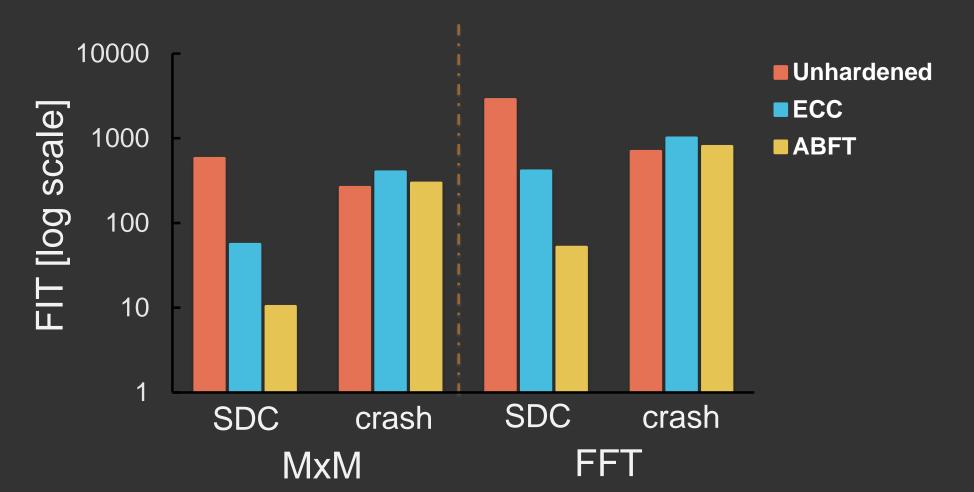

Parallel algorithms' reliability

SDC rates vary ~3 orders of magnitude

ECC reduces the SDC FIT of ~1 order of magnitude (there is almost no code dependence)

ECC increases the Crash FIT of about 50% (there is almost no code dependence)

When the ECC is ON Crashes are more likely to occur than SDCs (this is GOOD for HPC centers!)

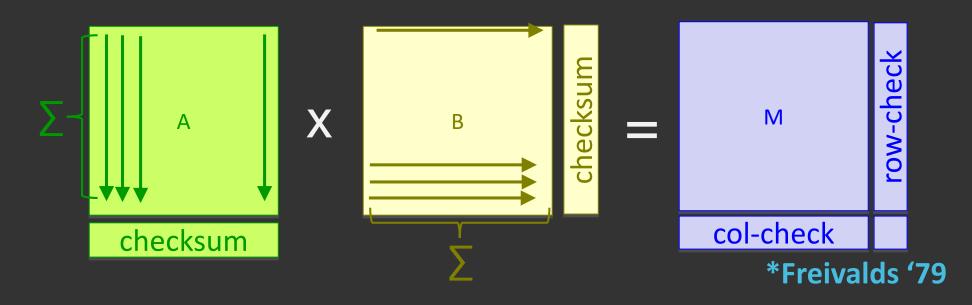

ABFT: technique designed specifically for an algorithm.

Usually ABFT requires input coding, algorithm modification, and output decoding with error detection/correction

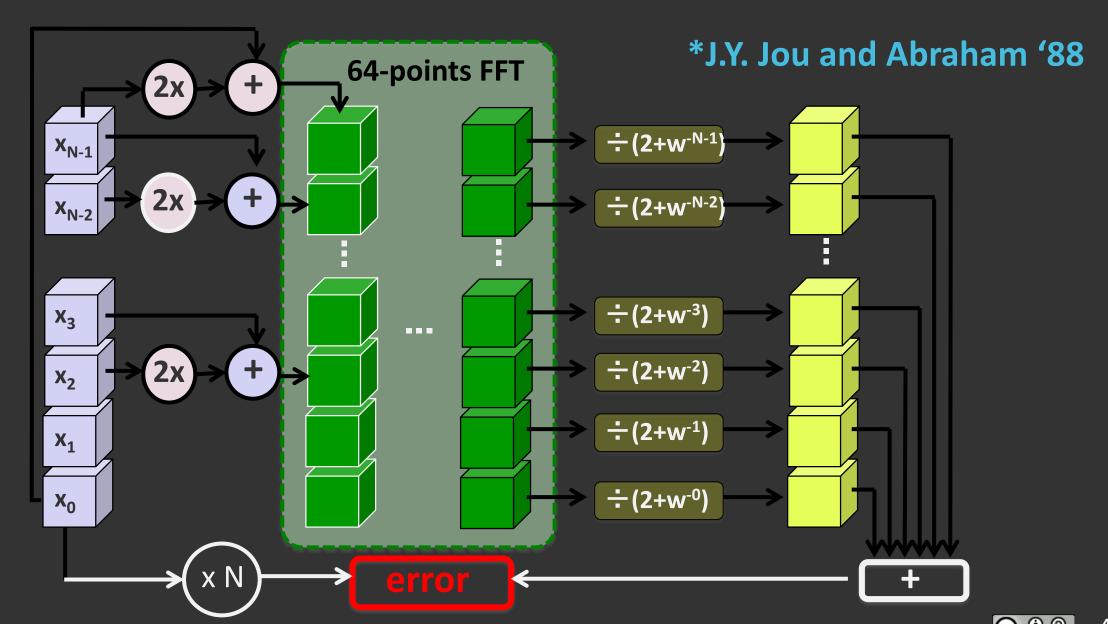

## Fault Tolerance Research – ABFT for FFT

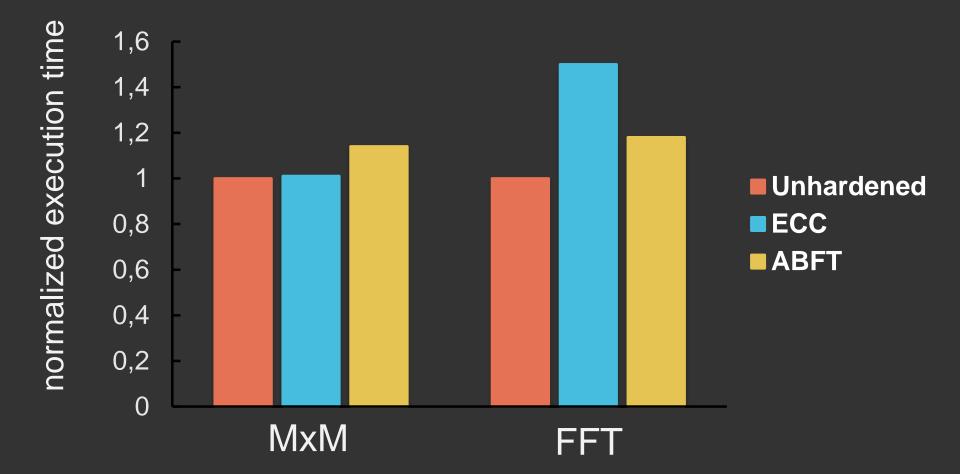

## **ECC x ABFT**

## ECC x ABFT

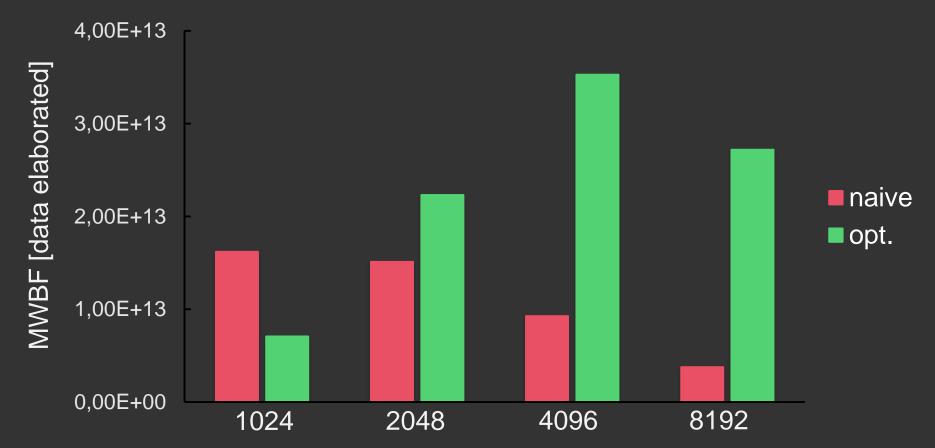

## Effects of optimizations: MxM

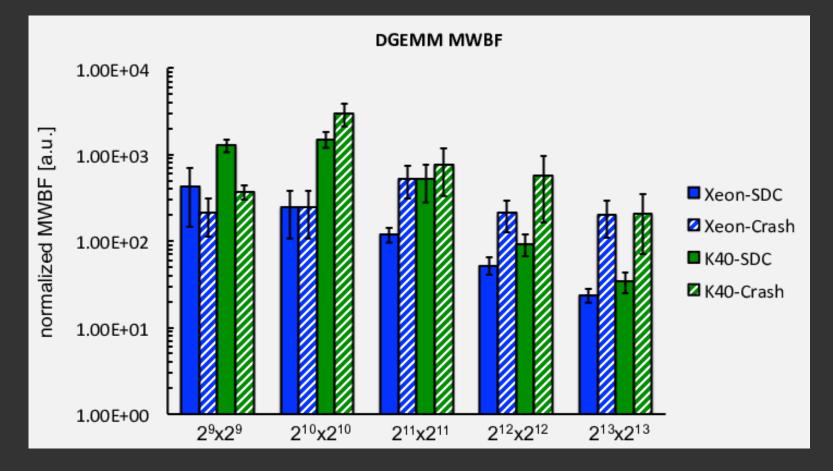

**MWBF: Mean Workload Between Failures**

Xeon-Phi MWBF decreases significantly with input size.

Even if more prone to be corrupted, Kepler produces more correct data (if parallelism is exploited)

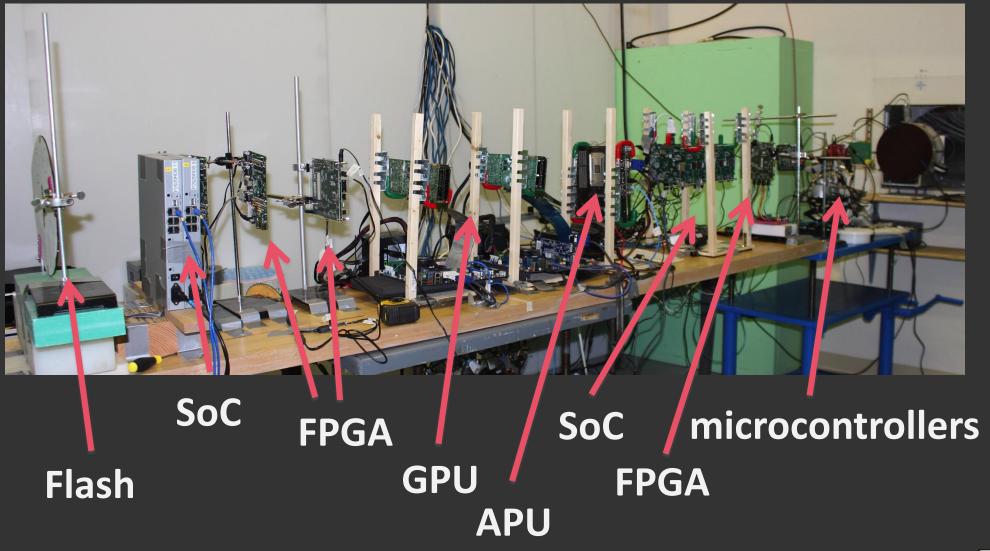

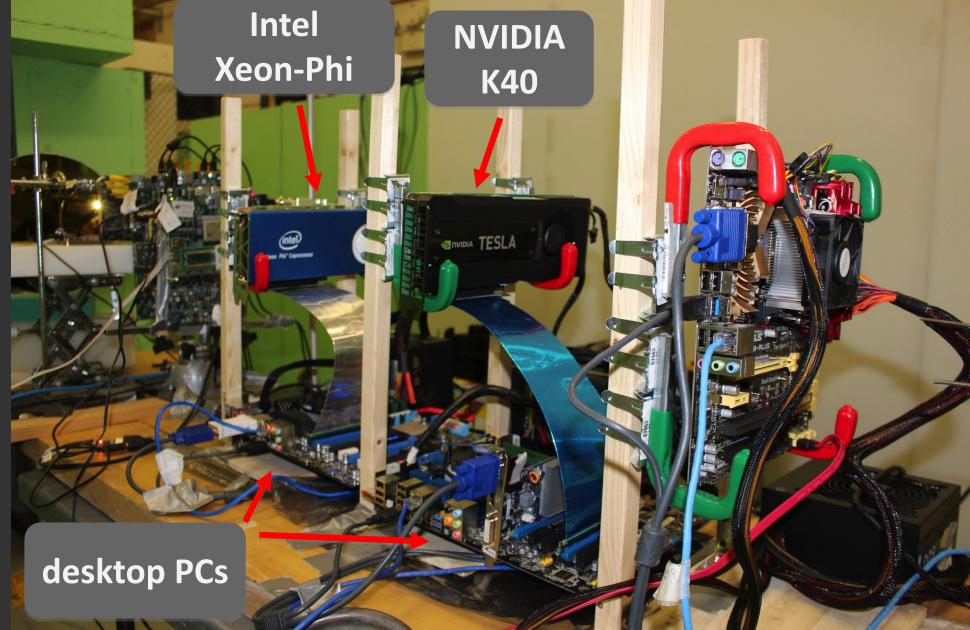

## **Fault Tolerance Interests**

- + applications & kernels for CPU & GPU

- + platforms for energy measurement

- + experiments with radiation

## Conclusions

### **Conclusions**

## EnergySFE

international collaboration

three research questions

lots of work in scheduling and fault tolerance

lots more to be done

# **Energy-aware Scheduling and Fault Tolerance Techniques for the Exascale Era**

Thank you.

Laércio Lima Pilla

laercio.pilla@ufsc.br

Federal University of Santa Catarina, Brazil